1. Allgemeine Informationen

Das Pluto-P ist ein FPGA-Board mit dem ACEX1K-Chip von Altera.

1.1. Anforderungen

-

Ein Pluto-P-Board

-

Ein EPP-kompatibler Parallelport, der im System-BIOS für den EPP-Modus konfiguriert ist, oder eine PCI-EPP-kompatible Parallelport-Karte.

|

Anmerkung

|

Das Pluto P Board benötigt den EPP-Modus. Netmos98xx-Chips funktionieren nicht im EPP-Modus. Die Pluto P Karte funktioniert auf einigen Computern und auf anderen nicht. Es gibt kein bekanntes Muster, welche Computer funktionieren und welche nicht. |

Weitere Informationen über PCI EPP kompatible Parallelport-Karten finden Sie auf der LinuxCNC Supported Hardware Seite im Wiki.

1.2. Verbinder

-

Bei der Auslieferung der Pluto-P-Platine ist der linke Steckverbinder vorgelötet, wobei sich der Schlüssel in der angegebenen Position befindet. Die anderen Anschlüsse sind unbestückt. Es scheint keinen standardmäßigen 12-poligen IDC-Stecker zu geben, aber einige der Stifte eines 16-poligen Steckers können von der Platine neben QA3/QZ3 herunterhängen.

-

Der untere und der rechte Anschluss befinden sich auf demselben .1"-Raster, der linke Anschluss jedoch nicht. Wenn OUT2…OUT9 nicht benötigt werden, kann ein einzelner IDC-Stecker den unteren Stecker und die unteren beiden Reihen des rechten Steckers überbrücken.

1.3. Physikalische Stifte (engl.+ inzwischen auch deutsch: pins)

-

Lesen Sie das ACEX1K-Datenblatt für Informationen über Eingangs- und Ausgangsspannungsschwellenwerte. Die Pins sind alle im LVTTL/LVCMOS Modus konfiguriert und sind generell mit 5V TTL-Logik kompatibel.

-

Vor der Konfiguration und nach dem ordnungsgemäßen Verlassen von LinuxCNC werden alle Pluto-P-Pins mit schwachen Pull-ups (20 kΩ min, 50 kΩ max) tristiert. Wenn der Watchdog-Timer aktiviert ist (Standardeinstellung), werden diese Pins auch nach einer Unterbrechung der Kommunikation zwischen LinuxCNC und der Karte tristiert. Der Watchdog-Timer benötigt etwa 6,5 ms, um aktiviert zu werden. Allerdings können Software-Fehler in der pluto_servo-Firmware oder LinuxCNC die Pluto-P-Pins in einem undefinierten Zustand lassen.

-

Im Modus PWM+RIchtung (engl. pwm+dir) ist Richtung (dir) standardmäßig HIGH für negative Werte und LOW für positive Werte. Um HIGH für positive Werte und LOW für negative Werte zu wählen, setzen Sie den entsprechenden Parameter dout-NN-invert auf TRUE, um das Signal zu invertieren.

-

Der Indexeingang wird mit der steigenden Flanke getriggert. Erste Tests haben gezeigt, dass die QZx-Eingänge besonders rauschempfindlich sind, da sie alle 25 ns abgefragt werden. Es wurde eine digitale Filterung hinzugefügt, um Impulse zu filtern, die kürzer als 175 ns (sieben Abfragezeiten) sind. Eine zusätzliche externe Filterung an allen Eingangspins, wie z. B. ein Schmitt-Puffer oder Inverter, ein RC-Filter oder ein Differentialempfänger (falls zutreffend) wird empfohlen.

-

Die Pins IN1…IN7 haben 22 Ω Vorwiderstände zu den entsprechenden FPGA-Pins. Keine anderen Pins haben irgendeine Art von Schutz für Spannungen oder Ströme außerhalb der Spezifikation. Es ist Sache des Integrators, eine geeignete Isolierung und einen entsprechenden Schutz hinzuzufügen. Herkömmliche Optoisolator-Karten mit parallelem Anschluss funktionieren aufgrund der bidirektionalen Natur des EPP-Protokolls nicht mit pluto_servo.

1.4. LED

-

Wenn das Gerät unprogrammiert ist, leuchtet die LED schwach. Wenn das Gerät programmiert ist, leuchtet die LED entsprechend dem Tastverhältnis von PWM0 (LED = UP0 xor DOWN0) oder STEPGEN0 (LED = STEP0 xor DIR0).

1.5. Power

-

Von VCC kann eine geringe Strommenge entnommen werden. Der verfügbare Strom hängt von der ungeregelten DC-Eingabe auf der Platine ab. Alternativ können dem FPGA über diese VCC-Pins regulierte +3,3 VDC zugeführt werden. Der erforderliche Strom ist noch nicht bekannt, liegt aber wahrscheinlich bei etwa 50 mA plus I/O-Strom.

-

Der Regler auf der Pluto-P-Platine ist ein Low-Dropout-Typ. Wenn 5 V an der Netzbuchse anliegen, kann der Regler ordnungsgemäß arbeiten.

1.6. PC-Schnittstelle

-

Es wird nur eine einzige pluto_servo oder pluto_step Karte unterstützt.

1.7. Neuerstellung der FPGA-Firmware

Die Unterverzeichnisse "src/hal/drivers/pluto_servo_firmware/" und "src/hal/drivers/pluto_step_firmware/" enthalten den Verilog-Quellcode sowie zusätzliche Dateien, die von Quartus für die FPGA-Firmware verwendet werden. Die Quartus II Software von Altera ist erforderlich, um die FPGA-Firmware neu zu erstellen. Um die Firmware aus den .hdl und anderen Quelldateien neu zu erstellen, öffnen Sie die .qpf Datei und drücken Sie CTRL-L. Dann kompilieren Sie LinuxCNC neu.

Wie der HAL-Hardwaretreiber unterliegt auch die FPGA-Firmware den Bedingungen der GNU General Public License.

Die kostenlose Version von Quartus II läuft nur unter Microsoft Windows, obwohl es offenbar eine kostenpflichtige Version gibt, die unter Linux läuft.

1.8. Für weitere Informationen

Einige zusätzliche Informationen dazu finden Sie unter KNJC LLC und unter Blog des Entwicklers.

2. Pluto-Servo

Das pluto_servo-System eignet sich für die Steuerung einer 4-Achsen-CNC-Fräse mit Servomotoren, einer 3-Achsen-Fräse mit PWM-Spindelsteuerung, einer Drehmaschine mit Spindel-Encoder, etc. Die große Anzahl von Eingängen ermöglicht einen vollständigen Satz von Endschaltern.

Dieser Treiber hat folgende Eigenschaften:

-

4 Quadraturkanäle mit 40 MHz Abtastrate. Die Zähler arbeiten im 4x Modus. Die maximale nützliche Quadratur-Rate ist 8191 Zählungen pro LinuxCNC Servo-Zyklus, oder etwa 8 MHz für LinuxCNC Standard 1 ms Servo-Rate.

-

4 PWM-Kanäle, up/down oder pwm+dir Stil. 4095 Arbeitszyklen von -100% bis +100%, einschließlich 0%. Die PWM-Periode beträgt etwa 19,5 kHz (40 MHz / 2047). Ein PDM-ähnlicher Modus ist ebenfalls verfügbar.

-

18 digitale Ausgänge: 10 dedizierte, 8 gemeinsam genutzte mit PWM-Funktionen. (Beispiel: Eine Drehmaschine mit unidirektionaler PWM-Spindelsteuerung kann insgesamt 13 digitale Ausgänge verwenden)

-

20 digitale Eingänge: 8 dedizierte, 12 gemeinsam genutzte mit Quadraturfunktionen. (Beispiel: Eine Drehmaschine mit Indeximpuls nur an der Spindel kann insgesamt 13 digitale Eingänge verwenden.)

-

EPP-Kommunikation mit dem PC. Die EPP-Kommunikation dauert bei den bisher getesteten Maschinen typischerweise etwa 100 µs und ermöglicht Servoraten über 1 kHz.

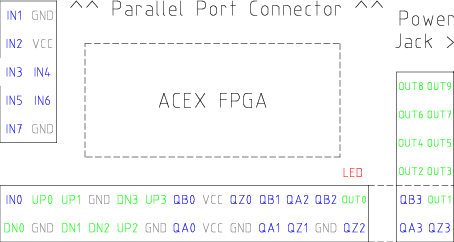

2.1. Pinbelegung

-

UPx - Das Up- (Aufwärts-/Abwärtsmodus) oder PWM-Signal (PWM+Richtung-Modus) vom PWM-Generator X. Kann als digitaler Ausgang verwendet werden, wenn der entsprechende PWM-Kanal unbenutzt ist oder der Ausgang des Kanals immer negativ ist. Der entsprechende digitale Ausgang kann auf TRUE gesetzt werden, damit UPx aktiv low statt aktiv high ist.

-

DNx - Das down- (Aufwärts/Abwärts-Modus) oder Richtungs-Signal (PWM+direction-Modus) vom PWM-Generator X. Kann als digitaler Ausgang verwendet werden, wenn der entsprechende PWM-Kanal unbenutzt ist oder der Ausgang des Kanals nie negativ ist. Der entsprechende digitale Ausgang kann auf TRUE gesetzt werden, damit DNx aktiv low statt aktiv high ist.

-

QAx, QBx - Die A- und B-Signale für Quadraturzähler X. Kann als digitaler Eingang verwendet werden, wenn der entsprechende Quadraturkanal nicht verwendet wird.

-

QZx - Das Z-Signal (Index) für Quadraturzähler X. Kann als digitaler Eingang verwendet werden, wenn die Indexfunktion des entsprechenden Quadraturkanals nicht verwendet wird.

-

INx - Dedizierter digitaler Eingang#x

-

OUTx - Dedizierter digitaler Ausgang #x

-

GND - Masse (engl. ground)

-

VCC' - +3,3V geregelter Gleichstrom (engl. regulated DC)

| Primäre Funktion | Alternative Funktion | Verhalten bei Verwendung beider Funktionen |

|---|---|---|

UP0 |

PWM0 |

Wenn pwm-0-pwmdir TRUE ist, dann ist dieser Pin der PWM-Ausgang |

OUT10 |

geXORt (engl. XOR’d) mit UP0 oder PWM0 |

|

UP1 |

PWM1 |

Wenn pwm-1-pwmdir TRUE ist, dann ist dieser Pin der PWM-Ausgang |

OUT12 |

geXORt mit UP1 oder PWM1 |

|

UP2 |

PWM2 |

Wenn pwm-2-pwmdir TRUE ist, dann ist dieser Pin der PWM-Ausgang |

OUT14 |

geXORt mit UP2 oder PWM2 |

|

UP3 |

PWM3 |

Wenn pwm-3-pwmdir TRUE ist, dann ist dieser Pin der PWM-Ausgang |

OUT16 |

geXORt mit UP3 oder PWM3 |

|

DN0 |

DIR0 |

Wenn pwm-0-pwmdir TRUE ist, dann ist dieser Pin der DIR-Ausgang |

OUT11 |

geXORt mit DN0 oder DIR0 |

|

DN1 |

DIR1 |

Wenn pwm-1-pwmdir TRUE ist, dann ist dieser Pin der DIR-Ausgang |

OUT13 |

geXORt mit DN1 oder DIR1 |

|

DN2 |

DIR2 |

Wenn pwm-2-pwmdir TRUE ist, dann ist dieser Pin der DIR-Ausgang |

OUT15 |

geXORt mit DN2 oder DIR2 |

|

DN3 |

DIR3 |

Wenn pwm-3-pwmdir TRUE ist, dann ist dieser Pin der DIR-Ausgang |

OUT17 |

geXORt mit DN3 oder DIR3 |

|

QZ0 |

IN8 |

Gleichen Wert lesen |

QZ1 |

IN9 |

Gleichen Wert lesen |

QZ2 |

IN10 |

Gleichen Wert lesen |

QZ3 |

IN11 |

Gleichen Wert lesen |

QA0 |

IN12 |

Gleichen Wert lesen |

QA1 |

IN13 |

Gleichen Wert lesen |

QA2 |

IN14 |

Gleichen Wert lesen |

QA3 |

IN15 |

Gleichen Wert lesen |

QB0 |

IN16 |

Gleichen Wert lesen |

QB1 |

IN17 |

Gleichen Wert lesen |

QB2 |

IN18 |

Gleichen Wert lesen |

QB3 |

IN19 |

Gleichen Wert lesen |

2.2. Input-Latching und Output-Aktualisierung

-

Die PWM-Tastverhältnisse werden für jeden Kanal zu unterschiedlichen Zeiten aktualisiert.

-

Die digitalen Ausgänge OUT0 bis OUT9 werden alle zur gleichen Zeit aktualisiert. Die digitalen Ausgänge OUT10 bis OUT17 werden gleichzeitig mit der PWM-Funktion aktualisiert, mit der sie geteilt werden.

-

Die digitalen Eingänge IN0 bis IN19 werden alle gleichzeitig gehalten (engl. latched).

-

Die Quadraturpositionen werden für jeden Kanal zu unterschiedlichen Zeiten gespeichert.

2.3. HAL-Funktionen, Pins und Parameter

Eine Liste aller loadrt-Argumente, HAL-Funktionsnamen, Pin-Namen und Parameter-Namen befindet sich in der Manpage zu pluto_servo.9.

2.4. Kompatible Treiber-Hardware

Ein Schaltplan für eine 2A, 2-Achsen-PWM-Servoverstärkerplatine ist von der (der Softwareentwickler) erhältlich. Die L298 H-Bridge kann für Motoren bis zu 4A (ein Motor pro L298) oder bis zu 2A (zwei Motoren pro L298) mit einer Versorgungsspannung von bis zu 46V verwendet werden. Der L298 verfügt jedoch nicht über eine eingebaute Strombegrenzung, was bei Motoren mit hohen Stillstandsströmen ein Problem darstellt. Für höhere Ströme und Spannungen haben einige Anwender über Erfolge mit den integrierten High-Side/Low-Side-Treibern von International Rectifier berichtet.

3. Pluto Step

Pluto-step ist für die Steuerung einer 3- oder 4-Achsen-CNC-Fräse mit Schrittmotoren geeignet. Die große Anzahl von Eingängen ermöglicht einen vollständigen Satz von Endschaltern.

Die Karte hat folgende Merkmale:

-

4 Schritt+Richtung-Kanäle mit 312,5 kHz maximaler Schrittrate, programmierbarer Schrittlänge, Abstand und Richtungswechselzeiten

-

14 dedizierte digitale Ausgänge

-

16 dedizierte digitale Eingänge

-

EPP-Kommunikation mit dem PC

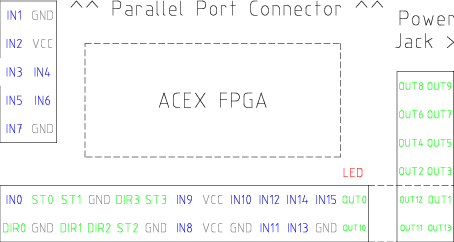

3.1. Pinbelegung

-

STEPx - Der Step (Clock) Ausgang des Stepgen-Kanals x

-

DIRx - Die Richtungs-Ausgabe des Stepgen-Kanals x

-

INx - Dedizierter digitaler Eingang#x

-

OUTx - Dedizierter digitaler Ausgang #x

-

GND - Masse (engl. ground)

-

VCC' - +3,3V geregelter Gleichstrom (engl. regulated DC)

Während der "erweiterte Hauptanschluss" über eine Reihe von Signalen verfügt, die normalerweise auf einem Step & Direction DB25-Anschluss zu finden sind - 4 Schrittgeneratoren, 9 Eingänge und 6 Allzweckausgänge -, unterscheidet sich das Layout dieses Anschlusses von dem eines standardmäßigen 26-poligen Flachbandkabels zu einem DB25-Anschluss.

3.2. Input-Latching und Output-Aktualisierung

-

Die Schrittfrequenzen für jeden Kanal werden zu unterschiedlichen Zeiten aktualisiert.

-

Die digitalen Ausgänge werden alle gleichzeitig aktualisiert.

-

Die digitalen Eingänge werden alle zur gleichen Zeit gehalten (engl. latched).

-

Feedback-Positionen werden für jeden Kanal zu unterschiedlichen Zeiten gespeichert.

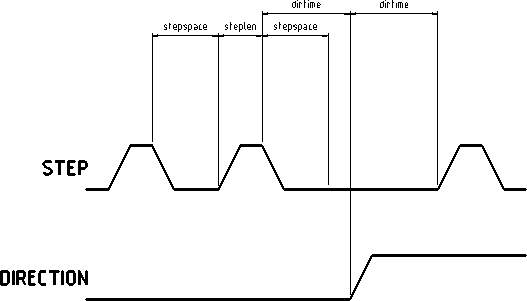

3.3. Schritt (engl. Step)-Wellenform-Timings

Die Firmware und der Treiber erzwingen Schrittlänge, Abstand und Richtungswechselzeiten. Die Zeiten werden auf das nächste Vielfache von 1,6 μs aufgerundet, mit einem Maximum von 49,6 μs. Die Zeitvorgaben sind dieselben wie bei der Softwarekomponente stepgen, mit der Ausnahme, dass "dirhold" und "dirsetup" zu einem einzigen Parameter "dirtime" zusammengefasst wurden, der das Maximum der beiden Parameter sein sollte, und dass für alle Kanäle stets dieselben Schrittvorgaben gelten.

3.4. HAL-Funktionen, Pins und Parameter

Eine Liste aller loadrt-Argumente, HAL-Funktionsnamen, Pin-Namen und Parameter-Namen findet sich in der Manpage zu pluto_step.9.